# PS200 Data Sheet

PowerSmart<sup>®</sup> Configurable Battery Charger

© 2005 Microchip Technology Inc.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, KEELOQ, MPLAB, PIC, PICmicro, PowerSmart and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

PowerCal, PowerInfo, PowerMate, PowerTool, Select Mode, Smart Serial and SmartTel are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

All other trademarks mentioned herein are property of their respective companies.

$\ensuremath{\textcircled{\sc 0}}$  2005, Microchip Technology Incorporated. Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

# **PS200**

# **PowerSmart® Configurable Battery Charger**

#### Features

- User configurable battery charger.

- Firmware available for the following cell chemistries:

- Lithium Ion/Polymer (available now)

- NiMH, NiCd (available Q2 2005)

- Pb Acid (available Q3 2005)

- 10-bit ADC for voltage, current and temperature measurement:

- Accurate Voltage Regulation (+/-1%)

- Accurate Current Regulation (+/-5%)

- Maximum integration for optimal size:

- Integrated voltage regulator

- Internal 8 MHz clock oscillator

- High-Frequency Switch mode charging configurable switching frequency up to 1 MHz

- 256 bytes EEPROM storage for charging parameters

- Switch mode charger supports buck and synchronous buck topologies

- · Configurable charge status display via two LEDs

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Power-saving Sleep mode

#### Applications

- Notebook Computers

- Personal Data Assistants

- Cellular Telephones

- Digital Still Cameras

- Camcorders

- Portable Audio Products

- Bluetooth<sup>®</sup> Devices

- Flashlights

- Power Tools

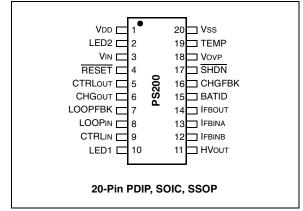

#### Pin Diagram

|     | Description | •        | i          |             | t                                                     |

|-----|-------------|----------|------------|-------------|-------------------------------------------------------|

| Pin | Pin Name    | Pin Type | Input Type | Output Type | Description                                           |

| 1   | Vdd         | Supply   | Power      | _           | Supply voltage                                        |

| 2   | LED2        | 0        | _          | CMOS        | Status indicator                                      |

| 3   | VIN         | I        | Analog     | _           | Battery voltage input                                 |

| 4   | RESET       | I        | ST         | _           | Reset                                                 |

| 5   | CTRLOUT     | 0        | _          | CMOS        | PWM output for setting current level                  |

| 6   | CHGOUT      | 0        | —          | CMOS        | PWM output to a buck converter for charge control     |

| 7   | LOOPFBK     | I        | Analog     |             | Current feedback loop                                 |

| 8   | LOOPIN      | I        | Analog     | _           | Current feedback loop input                           |

| 9   | CTRLIN      | Ι        | Analog     |             | Current level control                                 |

| 10  | LED1        | 0        | _          | CMOS        | Status indicator                                      |

| 11  | HVout       | 0        | _          | HVOD        | High-voltage, open-drain output pin (optional)        |

| 12  | Ifbinb      | Ι        | Analog     |             | Current feedback input pin B used for current scaling |

| 13  | Ifbina      | I        | Analog     |             | Current feedback input pin A used for current scaling |

| 14  | IFBOUT      | 0        | _          | Analog      | Current feedback output                               |

| 15  | BATID       | I        | Analog     |             | Battery ID select                                     |

| 16  | CHGFBK      | I        | Analog     |             | Charge control feedback                               |

| 17  | SHDN        | 0        | _          | Analog      | Shutdown signal, active-low                           |

| 18  | Vovp        | I        | Analog     | _           | Overvoltage protection                                |

| 19  | TEMP        | I        | Analog     | _           | Battery temperature input                             |

| 20  | Vss         | Supply   | Power      | _           | Supply ground                                         |

### **Pinout Description**

**Legend:** I = Input, O = Output, ST = Schmitt Trigger Input Buffer, HVOD = High-Voltage Open-Drain

# 1.0 PS200 OVERVIEW

The PS200 is a configurable Switch mode charger which is comprised of a PIC16F microcontroller core and precision analog circuitry. This section explores the hardware features in relation to generic Switch mode charging. Subsequent sections will describe the operation of the PS200 with firmware for Lithium-based (Section 2.0 "Lithium Chemistry Algorithm"), Nickel-based (Section 3.0 "Nickel Chemistry Algorithm") and Lead Acid (Section 4.0 "Lead Acid Chemistry Algorithm") charging.

- Oscillator

- Power-saving Sleep mode

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- High-Endurance Flash/EEPROM Cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM retention: > 40 years

- High-Speed Comparator module with:

- Two independent analog comparators

- Operational Amplifier module with two independent op amps

- Two-Phase Asynchronous Feedback PWM

- Voltage Regulator

- 10-bit (9-bit plus sign) A/D Converter

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

#### 1.1 Hardware Features

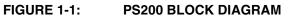

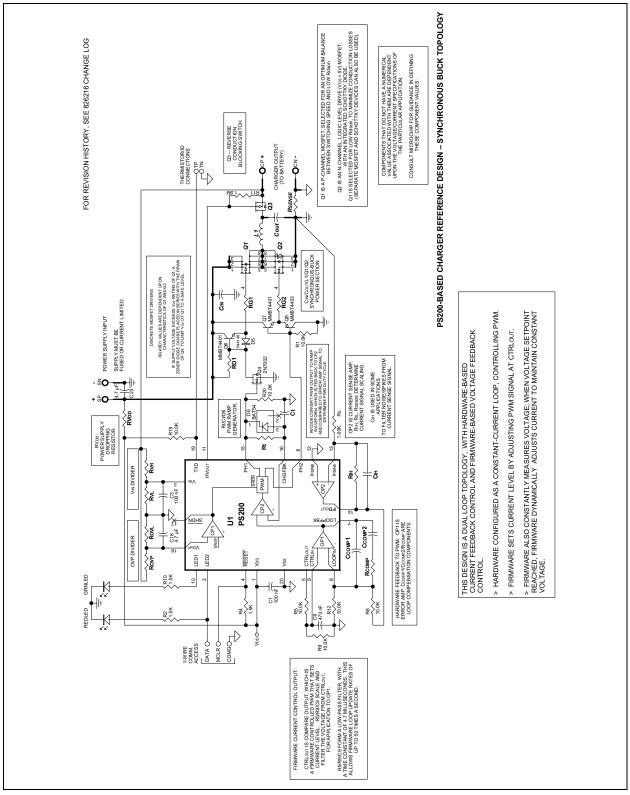

The PS200 features are well-suited for Switch mode battery charging. The PS200 device's block diagram (Figure 1-1) is to be used in conjunction with the Switch mode charger example (Figure 2-3, page 12).

Current/Voltage Measurement Block – The Current/Voltage Measurement Block consists of a 10-bit Analog-to-Digital converter, operational amplifiers and a comparator. The output of this block is fed into the Charge Control module. Please refer to Figure 1-1.

The inputs into this block are to be connected as described in Figure 2-3. The following signals are inputs into this block:

- LOOPFBK to comparator

- LOOPIN to op amp and ADC

- CTRLIN to op amp

- IFBINB to op amp

- IFBINA to op amp

- BATID to ADC

- TEMP to ADC

- CHGFBK to comparator

The following signals are outputs from this block:

- IFBOUT from op amp

- Charge Control Module:

- The charge control module generates a Pulse-Width Modulated signal called CHGOUT. Its frequency is configurable and can be set up to 1 MHz. This signal is connected to an external DC/DC buck converter.

- Voltage Regulator

- The integrated voltage regulator is designed to work with unregulated DC supplies.

- There are guidelines that should be followed. A series limiting resistor (RVDD) should be placed between the unregulated supply and the VDD pin. The value for this series resistor (RVDD) must be between RMIN and RMAX as shown in the following equation:

#### **EQUATION 1-1:**

$$RMAX = \frac{Vs(MIN) - 5V) * 1000}{1.05 * (16 mA + I(led))}$$

$$RMIN = \frac{Vs(MAX) - 5V) * 1000}{.95 * (50 \text{ mA})}$$

Where:

RMAX = maximum value of series resistor (ohms) RMIN = minimum value of series resistor (ohms)

Vs(MIN) = minimum value of charger DC supply (VDC) Vs(MAX) = maximum value of charger DC supply (VDC)

I(led) = total current drawn by all LEDs when illuminated simultaneously

The 1.05 and .95 constants are included to compensate for the tolerance of 5% resistors. The 16 mA constant is the anticipated load presented by the PS200, including the loading due to external components and a 4 mA minimum current for the shunt regulator itself. The 50 mA constant is the maximum acceptable current for the shunt regulator.

- The precision internal 8 MHz clock oscillator eliminates the need for external oscillator circuits.

- In-circuit configurability utilizing 256 bytes of on-board EEPROM.

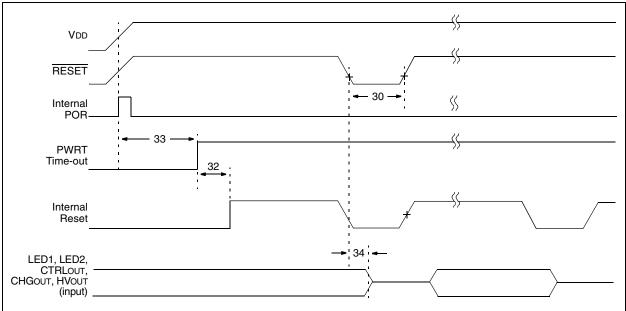

- Power on Reset The POR insures the proper start-up of the PS200 when voltage is applied to VDD.

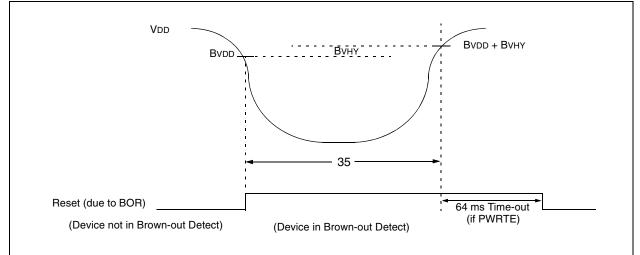

- Brown-out Reset The BOR is activated when the input voltage falls to 2.1V; the PS200 is reset.

# **PS200**

### 2.0 LITHIUM CHEMISTRY ALGORITHM

The PS200 provides an unprecedented level of configurability for charging Lithium Ion/Lithium Polymer battery packs. It's precision, 10-bit Analog-to-Digital converter and high-frequency Pulse-Width Modulator enable the PS200 to provide optimum control of charging algorithms for lithium battery chemistries. Special features include an internal voltage regulator and an internal clock oscillator that reduce external component count.

#### 2.1 Lithium Overview

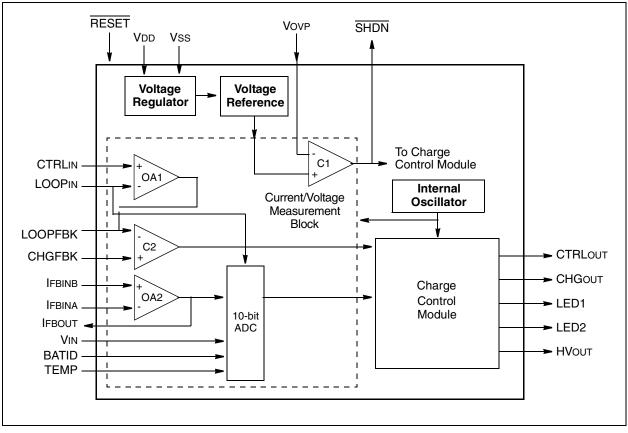

#### 2.1.1 MULTI-STEP CHARGING

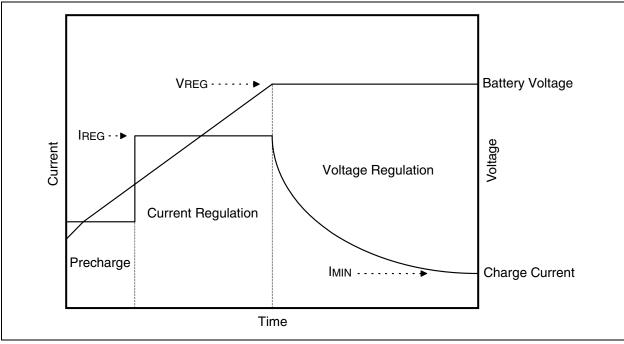

To ensure the proper treatment of lithium chemistries during extreme temperature and voltage conditions, multi-step charging is required. The PS200 starts the charging cycle upon sensing the presence of a battery pack and a valid charging supply. During charge qualification, the battery's temperature and voltage are measured to determine the appropriate initial state. The initial states include Charge Suspend, Precharge and Current Regulation. Charge Suspend halts charging when the user defined preset conditions for charging are not met. Precharge allows for the recovery of deeply discharged batteries by applying a low-charge current. Current Regulation provides constant current, voltage limited charge. Upon reaching the target voltage during Current Regulation, the Voltage Regulation state is entered. Charging continues at a constant voltage until the current decreases to the user specified minimum current threshold (VRIMin). At this threshold, charging is terminated and the End-Of-Charge state is reached.

The state diagram illustrates the charging cycle (see Figure 2-1).

#### 2.1.2 USER CONFIGURABLE PARAMETERS

The PS200 supports user configurable parameters that allow for customizing the charging profile. This feature allows for the maximum reuse of hardware, thus reducing time-to-market. These parameters include:

- Battery Temperature:

- Minimum/maximum temperature for charge initiation

- Maximum temperature allowed during charge

- Battery Voltage:

- Minimum/maximum voltage for charge initiation

- Target voltage during Voltage Regulation

- Voltage at which the charger will restart charging after completion of a valid charge cycle

- Charge Current:

- Target current during Current Regulation

- Taper current threshold for End-Of-Charge during Voltage Regulation

- Target current during Precharge

- Time:

- Precharge time limit

- Current Regulation time limit

- Voltage Regulation time limit

- Status Display:

- Two LEDs denote the charge states. Their flash rates can be modified.

# **PS200**

#### FIGURE 2-1: PS200 STATE DIAGRAM LI CHARGER

### 2.2 Lithium Charging

To ensure the proper treatment of lithium chemistries during extreme temperature and voltage conditions, multi-step charging is required. The PS200 measures key voltage, temperature and time parameters. It compares them to user defined voltage, temperature and time limits. These limits are described in **Section 2.4 "Lithium Configurable Parameters"**.

| Note: | Refer to    | Figure 2-1  | and    | Figure 2-2    | for |

|-------|-------------|-------------|--------|---------------|-----|

|       | clarificati | on when rea | ding t | this section. |     |

#### 2.2.1 CHARGE PENDING STATE – BEGINNING THE CHARGE CYCLE

The PS200 is initially set in the Charge Pending state (A). In this state, the presence of a battery pack must be sensed in order to begin the charging cycle. The PS200 comes up in the Charge Pending state, after a Reset, independent of the previous state.

#### 2.2.2 CHARGE QUALIFICATION STATE

During charge qualification, the battery's temperature and voltage are measured to determine the next charging state. There are four possible next states (see Figure 2-1).

- 1. If the battery's temperature is outside of the limits for charge initiation (TMAX, TMIN) then the next state is Charge Suspend (C).

- 2. If the battery's voltage is less than the minimum voltage for charge initiation (VMIN) and its temperature is within the limits for charge initiation (TMAX, TMIN), then the next state is Precharge (D).

- 3. If the battery's voltage is above the minimum voltage for charge initiation (VMIN) and its temperature is within the limits for charge initiation (TMAX, TMIN), then the next state is Current Regulation (E).

- 4. If the battery's voltage is above the voltage at which charging will restart (VRCHG), then the next state is Charge Complete (G).

#### 2.2.3 PRECHARGE STATE

The Precharge state allows for the recovery of a deeply discharged battery pack by applying a low charge rate. In this state, a user configured precharge current is applied to the battery, resulting in an increase in the battery's voltage (refer to Figure 2-2). There are three possible next states (see Figure 2-1).

- If the battery's voltage is above the minimum voltage for charge initiation (VMIN) and the battery's temperature is within the limits for charge initiation (TMAX, TMIN), then the next state is Current Regulation (E).

- 2. If the Precharge state time limit is exceeded (t<sub>p</sub>) and the battery's voltage remains less than the minimum voltage for charge initiation (VMIN), then the next state is Charge Suspend (C).

If the Precharge state time limit is exceeded  $(t_p)$  and the battery's temperature is greater than the maximum temperature for charge initiation (TMAX), then the next state is Charge Suspend (C).

If the Precharge state time limit is exceeded  $(t_p)$  and the battery's temperature is less than the minimum temperature for charge initiation (TMIN), then the next state is Charge Suspend (C).

If the battery pack is taken away (BATPRES = 0), then the PS200 enters the Charge Pending (A) state.

#### 2.2.4 CHARGE SUSPEND STATE

In the Charge Suspend state, no current is applied to the battery pack. There are two possible next states (see Figure 2-1).

- If the battery's temperature is within the limits for charge initiation (TMAX, TMIN) and its voltage is less than the voltage at which charging would restart (VRCHG), then the next state is Precharge (D).

- If the battery pack is taken away (BATPRES = 0), then the PS200 enters the Charge Pending (A) state.

#### 2.2.5 CURRENT REGULATION STATE

The Current Regulation state can be entered from the Precharge state or Charge Qualification state. Battery charging is initiated. This state provides constant current, voltage limited charging (refer to Figure 2-2). The charge current is referred to as IREG or the regulation current. While the current is applied, the battery's voltage increases until it reaches a voltage limit referred to as VREG or regulation voltage. Charging continues, during which battery voltage and temperature are monitored. There are three possible next states.

- If the battery's voltage reaches or exceeds the voltage limit, VREG and its temperature remains below the maximum allowable during current regulated charging (TMAXCHG), then the next state is Voltage Regulation (F).

- 2. If the battery exhibits any one of the following conditions then the next state is Charge Suspend (C):

- Battery voltage exceeds upper voltage limit for charging (VMAX)

- Battery temperature exceeds upper temperature limit for charging (TMAX)

- Battery temperature is below the lower temperature limit for charging (TMIN)

If the time in the Current Regulation state exceeds the time limit ( $t_i$ ), then the next state is Charge Suspend (C).

If the battery pack is taken away (BATPRES = 0), then the PS200 enters the Charge Pending (A) state.

#### 2.2.6 VOLTAGE REGULATION STATE

Voltage Regulation provides charging at a constant voltage while the charge current decreases (or tapers) to the user specified minimum current threshold (IMIN). There are three possible next states.

- 1. When the charge current reaches the taper current threshold for End-Of-Charge (IMIN) and the battery's voltage remains at the regulated voltage value (VREG), then the battery has reached the Charge Complete (G) state.

- If the battery exhibits any one of the following conditions, then the next state is Charge Suspend (C).

- Battery voltage exceeds upper voltage limit for charging (VMAX)

- Battery temperature exceeds upper temperature limit for charging (TMAXCHG)

If the time in the Voltage Regulation state exceeds the time limit  $(t_v)$ , then the next state is Charge Suspend (C).

If the battery pack is taken away (BATPRES = 0), then the PS200 enters the Charge Pending (A) state.

#### 2.2.7 CHARGE CYCLE COMPLETE STATE

The user specified minimum current threshold (IMIN) can be configured for various charging temperatures. At this threshold, charging is terminated and the End-Of-Charge state is reached. The PS200 can renew the charge cycle by entering the Charge Pending (A) state when: 1) the battery is removed (BATPRES = 0), or 2) if the battery's voltage falls below the recharge threshold voltage (VRCHG).

#### FIGURE 2-2: PS200 CHARGING PROFILE

# 2.3 KEELOQ<sup>®</sup> Algorithm

The PS200 includes Microchip's KEELOQ decoder algorithm. The KEELOQ code hopping technology is a worldwide standard providing a simple, yet highly secure, solution for authentication. Microchip's battery management products include the KEELOQ algorithm to provide secure identification for rechargeable batteries. When the KEELOQ algorithm is enabled, the PS200 will issue a 32-bit challenge to the attached rechargeable battery. The battery, which also includes the KEELOQ decoder algorithm, will generate a response. See Microchip application note AN827 "Using  $KEELOQ^{\textcircled{B}}$  to Validate Subsystem Compatibility" (DS00827) for details on implementing a complete KEELOQ battery authentication system.

#### 2.4 Lithium Configurable Parameters

The PS200 device's configurable parameters allow for flexible changes in designing battery chargers. The parameters are categorized as follows:

- Configuration

- Charging Limits

- Precharge

- Current Regulation

- Voltage Regulation

- LED Display Configuration

Please refer to Table 2-1 "PS200 Lithium Configurable Parameters".

#### 2.4.1 CONFIGURATION PARAMETERS

The configuration parameters provide an identity to the battery pack and provide its basic characteristics to the PS200.

#### 2.4.2 CHARGING LIMITS

#### 2.4.2.1 Precharge Parameters

The Precharge parameters configure the charger's operation during this initial battery charging phase.

#### 2.4.2.2 Current Regulation Parameters

The Current Regulation parameters configure the charger's operation during this second battery charging phase.

#### 2.4.2.3 Voltage Regulation Parameters

The Voltage Regulation parameters configure the charger's operation during this third battery charging phase.

#### 2.4.3 LED DISPLAY CONFIGURATION

The PS200 supports a two-LED charging state display. These LEDs can be configured to identify seven unique charger states:

- Charge Pending charger is waiting for battery pack that needs charge.

- Charge Qualification charger is determining if the battery pack can be safely charged.

- Precharge charger is charging the battery pack under the conditions configured for precharge.

- Charge Suspend charger has temporarily suspended charging the battery pack. This state is usually entered as a result of violating a maximum temperature requirement. Charging will resume when conditions are within required charging parameter values.

- Current Regulation charger is charging the battery pack with a constant current.

- Voltage Regulation charger is charging the battery pack at the constant target voltage.

- Charge Complete charger has completed charging the battery pack.

### TABLE 2-1: PS200 LITHIUM CONFIGURABLE PARAMETERS

| Step 1 – Configura | tion       |                |                |                  |                                                                                                                                                                                             |

|--------------------|------------|----------------|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter Name     | #<br>Bytes | Lower<br>Limit | Upper<br>Limit | Typical<br>Value | Description                                                                                                                                                                                 |

| MfgName            | _          | N/A            | N/A            | Microchip        | ASCII value.                                                                                                                                                                                |

| DevName            | _          | N/A            | N/A            | PS200            | ASCII value.                                                                                                                                                                                |

| SeriesCells        | 1          | 1              | 255            | 4                | Number of series connected cells in the battery pack.                                                                                                                                       |

| Capacity (mAh)     | 2          | 0              | 65535          | 2000             | Full-charge capacity of the battery pack.                                                                                                                                                   |

| PWMFreq            | 1          | 7              | 83             | 15               | LUT value which determines the PWM frequency.                                                                                                                                               |

| Step 2 – Charging  | Limits     |                |                |                  |                                                                                                                                                                                             |

| Parameter Name     | #<br>Bytes | Lower<br>Limit | Upper<br>Limit | Typical<br>Value | Description                                                                                                                                                                                 |

| PCVMin (mV)        | 2          | 0              | 65535          | 2500             | Minimum cell voltage required to enable charging with precharge conditions.                                                                                                                 |

| PCVMax (mV)        | 2          | 0              | 65535          | 3000             | Maximum cell voltage required to enable charging with<br>precharge conditions.                                                                                                              |

| PCCurrent (mA)     | 2          | 0              | 65535          | 200              | Charging current during precharge.                                                                                                                                                          |

| PCTempMin          | 1          | 0              | 255            | 50               | Minimum temperature required to enable charging with precharge conditions.<br>PCTempMin value = (temperature $^{\circ}C * 10 + 200)/4$ ; so typical value of 50 = 0 $^{\circ}C$ .           |

| PCTempMax          | 1          | 0              | 255            | 175              | Maximum temperature required to enable charging with precharge conditions.<br>PCTempMax value = (temperature °C * 10 + 200)/4; so typical value of 175 = 50°C.                              |

| PCTime (min)       | 1          | 0              | 255            | 60               | Duration of precharge.                                                                                                                                                                      |

| CRVTarg (mV)       | 2          | 0              | 65535          | 4200             | Target cell voltage in current regulation. This is set to the fully charged voltage of one cell, typically, as specified by the cell manufacturer.                                          |

| CRCurrent (mA)     | 2          | 0              | 65536          | 2000             | Charging current during current regulation.                                                                                                                                                 |

| CRTimeMax (min)    | 1          | 0              | 255            | 90               | Current regulation time limit.                                                                                                                                                              |

| VRVrech (mV)       | 2          | 0              | 65536          | 3780             | Voltage regulation recharge cell voltage. Charger will<br>automatically begin charging if cell voltage of pack falls below<br>SeriesCells * VRVrech.                                        |

| VRIMin (mA)        | 2          | 0              | 65536          | 150              | Voltage regulation fully charged current. This is the value of the taper current or IMIN which will determine that the battery is fully charged.                                            |

| VRTimeMax (min)    | 1          | 0              | 255            | 90               | Voltage regulation time limit.                                                                                                                                                              |

| TempMax            | 1          | 0              | 255            | 200              | Maximum temperature required to enable charging during<br>current regulation and voltage regulation.<br>TempMax value = (temperature °C $*$ 10 + 200)/4;<br>so typical value of 200 = 60°C. |

| Step 3 – LED Displ | Step 3 – LED Display |                |                |                  |                                                          |  |  |  |

|--------------------|----------------------|----------------|----------------|------------------|----------------------------------------------------------|--|--|--|

| Parameter Name     | #<br>Bytes           | Lower<br>Limit | Upper<br>Limit | Typical<br>Value | Description                                              |  |  |  |

| LED1Pending        | 1                    | N/A            | N/A            | 0b0000000        | LED1 display when charge is pending.                     |  |  |  |

| LED2Pending        | 1                    | N/A            | N/A            | 0b0000000        | LED2 display when charge is pending.                     |  |  |  |

| LED1Qual           | 1                    | N/A            | N/A            | 0b0000000        | LED1 display during charge qualification.                |  |  |  |

| LED2Qual           | 1                    | N/A            | N/A            | 0b0000000        | LED2 display during charge qualification.                |  |  |  |

| LED1PC             | 1                    | N/A            | N/A            | 0b0000000        | LED1 display during precharge.                           |  |  |  |

| LED2PC             | 1                    | N/A            | N/A            | 0b0000000        | LED2 display during precharge.                           |  |  |  |

| LED1Suspend        | 1                    | N/A            | N/A            | 0b0000000        | LED1 display when charge has been temporarily suspended. |  |  |  |

| LED2Suspend        | 1                    | N/A            | N/A            | 0b0000000        | LED2 display when charge has been temporarily suspended. |  |  |  |

| LED1CR             | 1                    | N/A            | N/A            | 0b0000000        | LED1 display during charge regulation.                   |  |  |  |

| LED2CR             | 1                    | N/A            | N/A            | 0b0000000        | LED2 display during charge regulation.                   |  |  |  |

| LED1VR             | 1                    | N/A            | N/A            | 0b0000000        | LED1 display during voltage regulation.                  |  |  |  |

| LED2VR             | 1                    | N/A            | N/A            | 0b0000000        | LED2 display during voltage regulation.                  |  |  |  |

| LED1Full           | 1                    | N/A            | N/A            | 0b0000000        | LED1 display when battery is fully charged.              |  |  |  |

| LED2Full           | 1                    | N/A            | N/A            | 0b0000000        | LED2 display when battery is fully charged.              |  |  |  |

| Miscellaneous      |                      |                |                |                  |                                                          |  |  |  |

| Parameter Name     | #<br>Bytes           | Lower<br>Limit | Upper<br>Limit | Typical<br>Value | Description                                              |  |  |  |

| PatternID          | 2                    | 0x0            | 0xFFFF         | 0x0              | Pattern ID.                                              |  |  |  |

| BatIDMin           | 1                    | 0              | 255            | 0                | BATID input pin value minimum.                           |  |  |  |

| BatIDMax           | 1                    | 0              | 255            | 255              | BATID input pin value maximum.                           |  |  |  |

### TABLE 2-1: PS200 LITHIUM CONFIGURABLE PARAMETERS (CONTINUED)

### 2.5 Lithium Application

Figure 2-3 is an example of the PS200 in a synchronous buck charger for Lithium Ion batteries. The sense resistor (RSENSE) is in a low side configuration. Refer to the Microchip web site (www.microchip.com) for the latest Application Notes that reference this theory of operation and component values.

FIGURE 2-3: SWITCH MODE CHARGER CIRCUIT EXAMPLE

# 3.0 NICKEL CHEMISTRY ALGORITHM

The PS200 algorithms for NiMH and NiCd chemistries are currently being developed.

# 4.0 LEAD ACID CHEMISTRY ALGORITHM

The PS200 algorithms for lead acid chemistries are currently being developed.

# **PS200**

NOTES:

# 5.0 ELECTRICAL SPECIFICATIONS

#### **Absolute Maximum Ratings†**

| Ambient temperature under bias                                                                                         | 40 to +125°C           |

|------------------------------------------------------------------------------------------------------------------------|------------------------|

| Storage temperature                                                                                                    | 65°C to +150°C         |

| Voltage on VDD with respect to Vss                                                                                     | 0.3 to +6.5V           |

| Voltage on RESET with respect to Vss                                                                                   | 0.3 to +13.5V          |

| Voltage on HVout with respect to Vss                                                                                   | 0V to +8.5V            |

| Voltage on all other pins with respect to Vss0.3                                                                       | 3V to (VDD + 0.3V)     |

| Total power dissipation <sup>(1)</sup>                                                                                 | 800 mW                 |

| Maximum current out of Vss pin                                                                                         | 300 mA                 |

| Maximum current into VDD pin                                                                                           | 250 mA                 |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                           | ±20 mA                 |

| Output clamp current, Iок (Vo < 0 or Vo >VDD)                                                                          | ±20 mA                 |

| Maximum output current sunk by any I/O pin                                                                             | 25 mA <sup>(2)</sup>   |

| Maximum output current sourced by each Port                                                                            | 50 mA <sup>(2)</sup>   |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\sum$ IOH} + $\sum$ {(VDD $-$ VOH) x IC | OH} + $∑$ (VOL x IOL). |

| 2. Total sources surrent must not exceed the abunt regulator conseits                                                  |                        |

**2:** Total source current must not exceed the shunt regulator capacity.

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 5.1 Reliability Targets

The device must be designed to target the following reliability specifications: ESD: ±4000V HBM ±400V MM all pins including VDD, Vss, RESET Latch-up: ±400 mA @ 125°C

#### 5.2 Design Targets

The AC/DC specifications included in the following sections are preliminary specifications that we intend to publish at product introduction. As the product matures, we intend to expand the specifications. Therefore, design should try and meet the following extended VDD/temperature targets:

- 1. Frequency of operation: DC 4 MHz, VDD = 2.0V 5.5V,  $-40^{\circ}C$  to  $125^{\circ}C$

- 2. Frequency of operation: DC 20 MHz, VDD = 4.5V 5.5V,  $-40^{\circ}C$  to  $125^{\circ}C$

#### 5.3 DC Characteristics

|                |      |                                                               |            | Standard Operating Conditions (unless otherwise stated)Operating temperature-40°C to +85°C |            |        |                                                      |  |  |

|----------------|------|---------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------|------------|--------|------------------------------------------------------|--|--|

| Param<br>No.   | Sym  | Characteristic                                                | Min        | Тур†                                                                                       | Max        | Units  | Conditions                                           |  |  |

| D001B<br>D001C | Vdd  | Supply Voltage                                                | 2.0<br>4.5 |                                                                                            | 5.0<br>5.0 | V<br>V | Fosc <= 4 MHz<br>Fosc > 4 MHz                        |  |  |

| D002           | Vdr  | RAM Data Retention Voltage <sup>(1)</sup>                     | 1.5*       |                                                                                            |            | V      | Device in Sleep mode                                 |  |  |

| D003           | VPOR | VDD Start Voltage to ensure<br>internal Power-on Reset signal | —          | Vss                                                                                        | _          | V      | See section on Power-on Reset for details            |  |  |

| D004           | Svdd | VDD Rise Rate to ensure internal<br>Power-on Reset signal     | 0.05*      | _                                                                                          | —          | V/ms   | See section on Power-on Reset for details            |  |  |

| D005           | VBOR | VDD Voltage required to initiate a<br>Brown-out Detect        | -          | 2.1                                                                                        | —          | V      |                                                      |  |  |

| D010S          | Idd  | Supply Current <sup>(2)</sup>                                 | —          | _                                                                                          | —          | mA     | VDD and current are constant due to shunt regulator. |  |  |

| D020           | IPD  | Power-Down Current <sup>(3)</sup>                             |            | 2.9                                                                                        | TBD        | nA     | VDD = 5.0V, WDT disabled                             |  |  |

**Legend:** TBD = To Be Determined

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested

- Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- 2: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD; RESET = VDD.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and VSS.

#### 5.4 Shunt Regulator

#### TABLE 5-1: SHUNT REGULATOR SPECIFICATIONS

| Shunt Regulator Specifications |               |      | onditions (unless otherwise stated)<br>-40°C to +125°C |      |       |                                        |  |  |

|--------------------------------|---------------|------|--------------------------------------------------------|------|-------|----------------------------------------|--|--|

| Characteristic                 | Sym           | Min  | Тур                                                    | Max  | Units | Comments                               |  |  |

| Shunt Voltage                  | VSHUNT        | 4.75 | —                                                      | 5.25 | Volts |                                        |  |  |

| Shunt Current                  | ISHUNT        | 4    | —                                                      | 50   | mA    |                                        |  |  |

| Shunt Resistance               | RSHUNT        |      | —                                                      | 3    | Ω     |                                        |  |  |

| Settling Time*                 | TSETTLE       | _    | —                                                      | 150  | ns    | To 1% of final value                   |  |  |

| Load Capacitance               | CLOAD         | 0.01 | —                                                      | 10   | μF    | Bypass capacitor on<br>VDD pin         |  |  |

| Regulator Operating Current    | $\Delta$ ISNT | _    | 180                                                    | —    | μA    | Includes band gap<br>reference current |  |  |

\* These parameters are characterized but not tested.

**Note:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

#### 5.5 DC Characteristics

| DC CHA       | RACTEI | RISTICS                                                           | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature -40°C to +85°C |      |         |       |                                                     |  |  |

|--------------|--------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|---------|-------|-----------------------------------------------------|--|--|

| Param<br>No. | Sym    | Characteristic                                                    | Min                                                                                             | Тур† | Мах     | Units | Conditions                                          |  |  |

| D032         | VIL    | Input Low Voltage<br>RESET                                        | Vss                                                                                             | _    | 0.2 Vdd | v     | $4.5V \le VDD \le 5.5V$ , otherwise entire range    |  |  |

| D042         | Viн    | Input High Voltage<br>RESET                                       | 0.8 Vdd                                                                                         | _    | Vdd     | v     | $4.5V \le VDD \le 5.5V$ ,<br>otherwise entire range |  |  |

|              | lı∟    | Input Leakage Current <sup>(2)</sup>                              |                                                                                                 |      |         |       |                                                     |  |  |

| D060A        |        | Analog inputs                                                     | _                                                                                               | ±0.1 | ±1      | μA    | $Vss \leq V PIN \leq V DD$                          |  |  |

| D061         |        | RESET <sup>(1)</sup>                                              | —                                                                                               | ±1   | ±5      | μA    | $Vss \leq V PIN \leq V DD$                          |  |  |

| D080         | Vol    | Output Low Voltage<br>Pins LED1, LED2, CTRLout,<br>CHGout, HVout  | _                                                                                               | _    | 0.6     | v     | IOL = 8.5 mA, VDD = 4.5V                            |  |  |

| D090         | Vон    | Output High Voltage<br>Pins LED1, LED2, CTRLOUT,<br>CHGOUT, HVOUT | Vdd - 0.7                                                                                       |      | _       | V     | Юн = -3.0 mA, VDD = 4.5V                            |  |  |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The leakage current on the RESET pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

2: Negative current is defined as current sourced by the pin.

#### 5.6 DC Characteristics

|              |      |                                            |      | Standard Operating Conditions (unless otherwise stated)Operating temperature-40°C to +85°C |     |       |                                     |  |  |

|--------------|------|--------------------------------------------|------|--------------------------------------------------------------------------------------------|-----|-------|-------------------------------------|--|--|

| Param<br>No. | Sym  | Characteristic                             | Min  | Тур†                                                                                       | Max | Units | Conditions                          |  |  |

|              |      | Capacitive Loading Specs<br>on Output Pins |      |                                                                                            |     |       |                                     |  |  |

| D101         | Cio  | Pins LED1, LED2, CTRLOUT,<br>CHGOUT, HVOUT | —    | —                                                                                          | 50* | pF    |                                     |  |  |

|              |      | Data EEPROM Memory                         |      |                                                                                            |     |       |                                     |  |  |

| D120         | ED   | Endurance                                  | 1M   | 10M                                                                                        | _   | E/W   | 25°C at 5V                          |  |  |

| D121         | Vdrw | VDD for read/write                         | VMIN | —                                                                                          | 5.5 | V     | Vмın = Minimum operating<br>voltage |  |  |

| D122         | TDEW | Erase/Write cycle time                     | —    | 5                                                                                          | 6   | ms    |                                     |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 5.7 AC Characteristics: PS200 (Industrial)

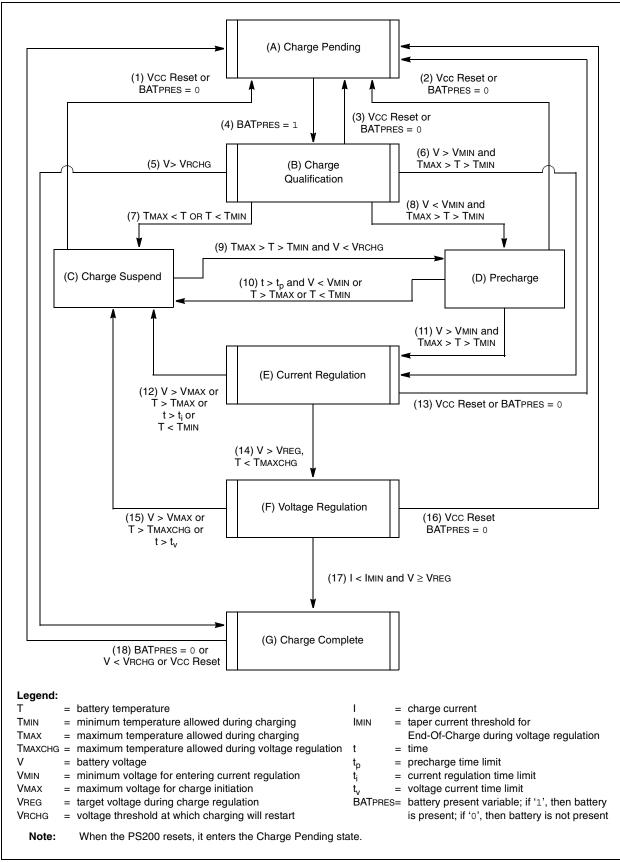

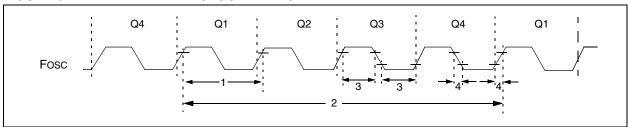

#### FIGURE 5-1: EXTERNAL CLOCK TIMING

#### TABLE 5-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                      | Min | Тур† | Max | Units | Conditions                      |

|--------------|------|-------------------------------------|-----|------|-----|-------|---------------------------------|

|              | Fosc | Oscillator Frequency <sup>(1)</sup> | _   | 8    | _   | MHz   | Using PS200 internal oscillator |

| 1            | Tosc | Oscillator Period <sup>(1)</sup>    | —   | 125  | _   | ns    | Using PS200 internal oscillator |

† Data in "Typ" column is at 5 V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

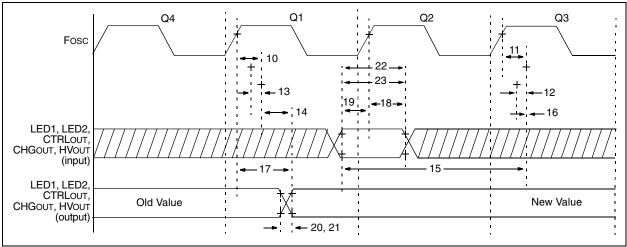

| TABLE 5-3: | CLKO AND I/O TIMING REQUIREMENTS |

|------------|----------------------------------|

|------------|----------------------------------|

| Param<br>No. | Sym      | Characteristic                                                | Min | Тур† | Мах  | Units | Conditions |

|--------------|----------|---------------------------------------------------------------|-----|------|------|-------|------------|

| 17           | TosH2ioV | Fosc ↑ (Q1 cycle) to Port Out Valid                           |     | 50   | 150* | ns    |            |

|              |          |                                                               | —   | _    | 300  | ns    |            |

| 18           | TosH2iol | Fosc ↑ (Q2 cycle) to Port Input<br>Invalid (I/O in hold time) | 100 |      |      | ns    |            |

| 19           | TioV2osH | Port Input Valid to Fosc 1<br>(I/O in setup time)             | 0   | —    | _    | ns    |            |

| 20           | TioR     | Port Output Rise Time                                         |     | 10   | 40   | ns    |            |

| 21           | TioF     | Port Output Fall Time                                         | _   | 10   | 40   | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0 V, 25°C unless otherwise stated.

#### FIGURE 5-4: BROWN-OUT DETECT TIMING AND CHARACTERISTICS

# TABLE 5-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT DETECT REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                               | Min        | Тур†      | Max         | Units    | Conditions                                                            |

|--------------|-------|--------------------------------------------------------------|------------|-----------|-------------|----------|-----------------------------------------------------------------------|

| 30           | ТмсL  | RESET Pulse Width (low)                                      | 2<br>11    |           | <br>24      | μs<br>ms | $VDD = 5V$ , $-40^{\circ}C$ to $+85^{\circ}C$<br>Extended temperature |

| 32           | Tost  | Oscillation Start-up Timer Period                            |            | 1024 Tosc |             |          | Tosc = Fosc period                                                    |

| 33*          | TPWRT | Power-up Timer Period<br>(4 x TwDT)                          | 28*<br>TBD | 64<br>TBD | 132*<br>TBD | ms<br>ms | VDD = 5V, -40°C to +85°C                                              |

| 34           | Tioz  | I/O High-Impedance from RESET<br>Low or Watchdog Timer Reset | —          | —         | 2.0         | μs       |                                                                       |

|              | Bvdd  | Brown-out Detect Voltage                                     | 2.025      |           | 2.175       | V        |                                                                       |

|              | Вуну  | Brown-out Hysteresis                                         |            | 25        |             | mV       |                                                                       |

| 35           | TBOR  | Brown-out Detect Pulse Width                                 | 100*       | —         |             | μs       | $V$ DD $\leq$ BVDD (D005)                                             |

**Legend:** TBD = To Be Determined

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| TABLE 5-5: | PRECISION INTERNAL OSCILLATOR PARAMETERS |

|------------|------------------------------------------|

|            |                                          |

| Param<br>No. | Sym  | Characteristic                                             | Freq<br>Tolerance | Min | Тур† | Max | Units | Conditions                                                                   |                            |

|--------------|------|------------------------------------------------------------|-------------------|-----|------|-----|-------|------------------------------------------------------------------------------|----------------------------|

| F10          | Fosc | OSC Internal Calibrated<br>INTOSC Frequency <sup>(1)</sup> | ±1%               | —   | 8.00 | TBD | MHz   | VDD and Temperature (TBD)                                                    |                            |

|              |      |                                                            | ±2%               | —   | 8.00 | TBD | MHz   | $2.5V \le VDD \le 5.5V$<br>$0^{\circ}C \le TA \le +85^{\circ}C$              |                            |

|              |      |                                                            | ±5%               | —   | 8.00 | TBD | MHz   | 2.0V ≤ VDD ≤ 5.5V<br>-40°C ≤ TA ≤ +85°C (Ind.)<br>-40°C ≤ TA ≤ +125°C (Ext.) |                            |

| F14          |      | TIOSCST Oscillator Wake-up from                            | -                 | —   |      | TBD | TBD   | μs                                                                           | VDD = 2.0V, -40°C to +85°C |

|              |      | Sleep Start-up Time*                                       | —                 | _   | TBD  | TBD | μs    | VDD = 3.0V, -40°C to +85°C                                                   |                            |

|              |      |                                                            | —                 | _   | TBD  | TBD | μs    | $VDD = 5.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                          |                            |

**Legend:** TBD = To Be Determined

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and .01  $\mu$ F values in parallel are recommended.

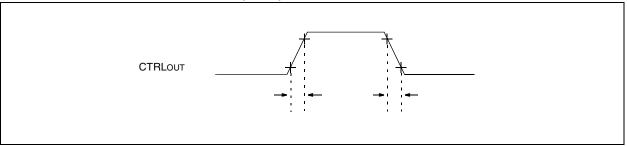

FIGURE 5-5: CTRLOUT TIMINGS (PIN 5)

#### TABLE 5-6: CTRLOUT REQUIREMENTS

| Param<br>No. | Sym  | Characteristic           | Min | Тур† | Max | Units | Conditions |

|--------------|------|--------------------------|-----|------|-----|-------|------------|

| 53*          | TccR | CTRLO∪⊤ Output Rise Time |     | 25   | 50  | ns    |            |

| 54*          | TccF | CTRLO∪⊤ Output Fall Time |     | 25   | 45  | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### 5.8 Current Voltage Measurement Block

| DC СН        | DC CHARACTERISTICS |                                                                                |                              | Standard Operating Conditions (unless otherwise stated)<br>VDD = 2.7V to 5.5V, TA = 25°C, VCM = VDD/2,<br>$RL = 100 k\Omega$ to VDD/2 and VOUT ~ VDD/2<br>Operating Temperature -40°C to +85°C for Industrial |                 |          |                                                                            |  |  |

|--------------|--------------------|--------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|----------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym                | Parameters                                                                     | Min Typ Max Units Conditions |                                                                                                                                                                                                               |                 |          |                                                                            |  |  |

| 001          | Vos                | Input Offset Voltage                                                           |                              | ±5                                                                                                                                                                                                            | —               | mV       |                                                                            |  |  |

| 002<br>003   | IB<br>IOS          | Input Current and Impedance<br>Input Bias Current<br>Input Offset Bias Current |                              | ±2*<br>±1*                                                                                                                                                                                                    |                 | nA<br>pA |                                                                            |  |  |

| 004<br>005   | Vсм<br>CMR         | <b>Common Mode</b><br>Common Mode Input Range<br>Common Mode Rejection         | Vss<br>TBD                   | —<br>70                                                                                                                                                                                                       | VDD – 1.4       | V<br>dB  | VDD = 5V<br>VCM = VDD/2, Frequency = DC                                    |  |  |

| 006A<br>006B | Aol<br>Aol         | <b>Open-Loop Gain</b><br>DC Open-Loop Gain<br>DC Open-Loop Gain                | _                            | 90<br>60                                                                                                                                                                                                      |                 | dB<br>dB | No load<br>Standard load                                                   |  |  |

| 007<br>008   | Vout<br>Isc        | Output<br>Output Voltage Swing<br>Output Short Circuit Current                 | Vss + 50<br>—                | <br>25                                                                                                                                                                                                        | VDD – 50<br>TBD | mV<br>mA | To VDD/2 (20 k $\Omega$ connected to VDD,<br>20 k $\Omega$ + 20 pF to Vss) |  |  |

| 010          | PSR                | Power Supply<br>Power Supply Rejection                                         | 80                           |                                                                                                                                                                                                               | _               | dB       |                                                                            |  |  |

# TABLE 5-7:DC CHARACTERISTICS (PINS LOOPIN, CTRLIN, IFBINB, IFBINA INPUTS;<br/>PIN IFBOUT OUTPUT)

**Legend:** TBD = To Be Determined

\* These parameters are characterized but not tested.

# TABLE 5-8:AC CHARACTERISTICS (PINS LOOPIN, CTRLIN, IFBINB, IFBINA INPUTS;<br/>PIN IFBOUT OUTPUT)

| AC CHARACTERISTICS |      |                        | Standard Operating Conditions (unless otherwise stated)<br>$VDD = 2.7V$ to 5.5V, $VSS = GND$ , $TA = 25^{\circ}C$ , $VCM = VDD/2$ ,<br>$RL = 100 k\Omega$ to $VDD/2$ and $VOUT = VDD/2$<br>Operating Temperature -40°C to +85°C for Industrial |     |     |         |            |  |

|--------------------|------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|------------|--|

| Param<br>No.       | Sym  | Parameters             | Min Typ Max Units Conditions                                                                                                                                                                                                                   |     |     |         | Conditions |  |

| 011                | GBWP | Gain Bandwidth Product | —                                                                                                                                                                                                                                              | 3   |     | MHz     | VDD = 5V   |  |

| 012                | TON  | Turn-on Time           | —                                                                                                                                                                                                                                              | 10  | TBD | μs      | VDD = 5V   |  |

| 013                | Θм   | Phase Margin           | —                                                                                                                                                                                                                                              | 60  |     | degrees | VDD = 5V   |  |

| 014                | SR   | Slew Rate              | 2                                                                                                                                                                                                                                              | TBD |     | V/µs    | VDD = 5V   |  |

Legend: TBD = To Be Determined

#### COMPARATOR SPECIFICATIONS (PINS LOOPFBK, CHGFBK, SHDN, VOVP) **TABLE 5-9:**

| Comparator Specifications |        |                                | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |     |            |          |                           |

|---------------------------|--------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|------------|----------|---------------------------|

| Param<br>No.              | Symbol | Characteristics                | Min                                                                                                                  | Тур | Мах        | Units    | Comments                  |

| C01                       | Vos    | Input Offset Voltage           | —                                                                                                                    | ± 2 | ± 5        | mV       |                           |

| C02                       | Vсм    | Input Common Mode Voltage      | 0                                                                                                                    | _   | Vdd - 1.5  | V        |                           |

| C03                       | ILC    | Input Leakage Current          |                                                                                                                      |     | 200*       | nA       |                           |

| C04                       | CMRR   | Common Mode Rejection<br>Ratio | +70*                                                                                                                 | —   | —          | dB       |                           |

| C05                       | Trt    | Response Time <sup>(1)</sup>   |                                                                                                                      | _   | 20*<br>40* | ns<br>ns | Internal<br>Output to pin |

These parameters are characterized but not tested.

Response time measured with one comparator input at (VDD - 1.5)/2, while the other input transitions from Note 1: Vss to VDD - 1.5V.

| TABLE 5-10: | COMPARATOR VOLTAGE REFERENCE | (VREF) | SPECIFICATIONS |

|-------------|------------------------------|--------|----------------|

|             |                              |        |                |

| Comparator Voltage Reference Specifications |        |                              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                   |                |            |                                             |

|---------------------------------------------|--------|------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------|----------------|------------|---------------------------------------------|

| Param<br>No.                                | Symbol | Characteristics              | Min                                                                                                                  | Тур               | Max            | Units      | Comments                                    |

| CV01                                        | CVRES  | Resolution                   | —                                                                                                                    | VDD/24*<br>VDD/32 | _              | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV02                                        |        | Absolute Accuracy            | _                                                                                                                    | _                 | ±1/4*<br>±1/2* | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV03                                        |        | Unit Resistor Value (R)      | —                                                                                                                    | 2K*               | _              | Ω          |                                             |

| CV04                                        |        | Settling Time <sup>(1)</sup> |                                                                                                                      | —                 | 10*            | μs         |                                             |

\* These parameters are characterized but not tested.

**Note 1:** Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

| IADEL J-II.  |      | AD CONVENTEN ONANACTENISTICS                         |                           |                           |                     |       |                                                                        |  |  |

|--------------|------|------------------------------------------------------|---------------------------|---------------------------|---------------------|-------|------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym  | Characteristic                                       | Min                       | Тур†                      | Мах                 | Units | Conditions                                                             |  |  |

| A01          | NR   | Resolution                                           |                           |                           | 10 bits             | bit   |                                                                        |  |  |

| A02          | EABS | Total Absolute Error*(1)                             | _                         | —                         | ±1                  | LSb   | VREF = 5.0V                                                            |  |  |

| A03          | EIL  | Integral Error                                       | —                         | —                         | ±1                  | LSb   | VREF = 5.0V                                                            |  |  |

| A04          | Edl  | Differential Error                                   | —                         | —                         | ±1                  | LSb   | No missing codes to 10 bits,<br>VREF = 5.0V                            |  |  |

| A05          | Efs  | Full-Scale Range                                     | 2.2*                      | —                         | 5.5*                | V     |                                                                        |  |  |

| A06          | EOFF | Offset Error                                         |                           | —                         | ±1                  | LSb   | VREF = 5.0V                                                            |  |  |

| A07          | Egn  | Gain Error                                           |                           | —                         | ±1                  | LSb   | VREF = 5.0V                                                            |  |  |

| A10          | —    | Monotonicity                                         | —                         | guaranteed <sup>(2)</sup> | —                   | _     | $VSS \le VAIN \le VREF$                                                |  |  |

| A20<br>A20A  | VREF | Reference Voltage                                    | 2.2 <sup>(4)</sup><br>2.5 | —                         | <br>Vdd + 0.3       | V     | Absolute minimum to ensure<br>10-bit accuracy                          |  |  |

| A25          | VAIN | Analog Input Voltage                                 | Vss                       |                           | VREF <sup>(5)</sup> | V     |                                                                        |  |  |

| A30          | ZAIN | Recommended<br>Impedance of Analog<br>Voltage Source | —                         | _                         | 10                  | kΩ    |                                                                        |  |  |

| A50          | IREF | VREF Input Current* <sup>(3)</sup>                   | 10                        |                           | 1000                | μA    | During VAIN acquisition.<br>Based on differential of VHOLD<br>to VAIN. |  |  |

|              |      |                                                      | —                         | —                         | 10                  | μA    | During A/D conversion cycle.                                           |  |  |

#### TABLE 5-11: A/D CONVERTER CHARACTERISTICS

\* These parameters are characterized but not tested.

† Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes Integral, Differential, Offset and Gain Errors.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

3: VREF current is from external VREF or VDD pin, whichever is selected as reference input.

4: Only limited when VDD is at or below 2.5V. If VDD is above 2.5V, VREF is allowed to go as low as 1.0V.

5: Analog input voltages are allowed up to VDD, however, the conversion accuracy is limited to VSS to VREF.

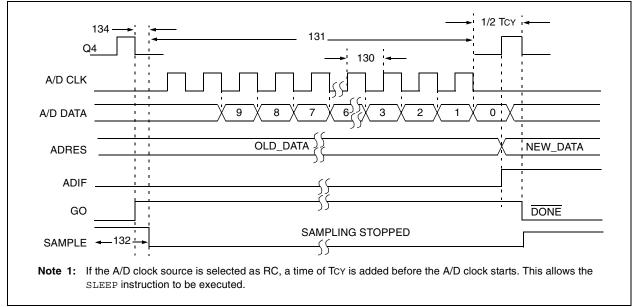

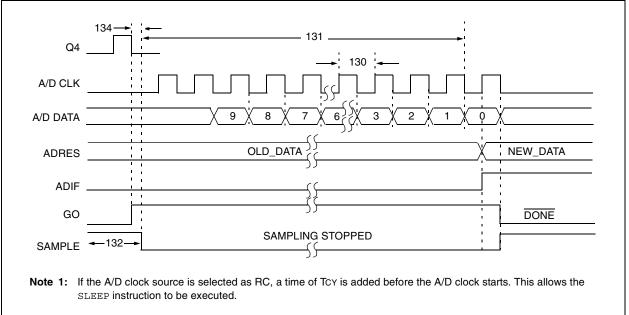

#### FIGURE 5-6: A/D CONVERSION TIMING (NORMAL MODE)

# **PS200**

| TABLE 5-12:  |      | A/D CONVERSION REQUIREMENTS                                           |      |        |      |       |                                                                                                                                                                                                                             |  |  |

|--------------|------|-----------------------------------------------------------------------|------|--------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym  | Characteristic                                                        | Min  | Тур†   | Мах  | Units | Conditions                                                                                                                                                                                                                  |  |  |

| 130*         | Tad  | A/D Clock Period                                                      | 1.6  | _      |      | μs    | Tosc based, V <sub>REF</sub> ≥ 2.5V                                                                                                                                                                                         |  |  |

|              |      |                                                                       | 3.0* | —      | —    | μs    | TOSC based, VREF full range                                                                                                                                                                                                 |  |  |

| 130*         | Tad  | A/D Internal RC<br>Oscillator Period                                  | 3.0* | 6.0    | 9.0* | μs    | ADCS<1:0> = 11 (RC mode)<br>At V <sub>DD</sub> = 2.5V                                                                                                                                                                       |  |  |

|              |      |                                                                       | 2.0* | 4.0    | 6.0* | μs    | At VDD = 5.0V                                                                                                                                                                                                               |  |  |

| 131*         | ΤΟΝΥ | Conversion Time<br>(not including<br>acquisition time) <sup>(1)</sup> | _    | 11 Tad | _    | TAD   | Set GO bit to new data in<br>A/D Result register                                                                                                                                                                            |  |  |

| 132*         | TACQ | Acquisition Time                                                      | —    | 11.5   |      | μs    |                                                                                                                                                                                                                             |  |  |

|              |      |                                                                       | 5*   | _      | _    | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.,<br>1 mV @ 4.096V) from the last<br>sampled voltage (as stated on<br>CHOLD). |  |  |

| 134*         | TGO  | Q4 to A/D Clock<br>Start                                              | _    | Tosc/2 |      | —     | If the A/D clock source is selected<br>as RC, a time of TCY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                |  |  |

#### TABLE 5-12: A/D CONVERSION REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

### 6.0 PACKAGING INFORMATION

#### 6.1 Package Marking Information

#### 20-Lead SSOP

|   | Example |           |  |  |  |  |  |

|---|---------|-----------|--|--|--|--|--|

|   | PS      | 6200/SO@3 |  |  |  |  |  |

|   | 5       | 0510017   |  |  |  |  |  |

| 0 |         |           |  |  |  |  |  |

#### Example

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|-------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carrie                                 | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                            |

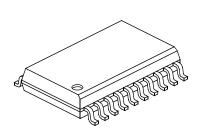

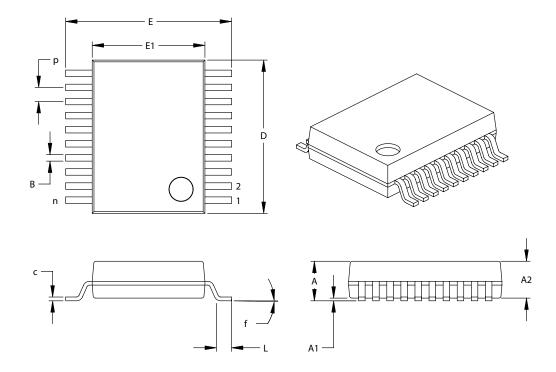

#### 6.2 **Package Details**

The following sections give the technical details of the packages.

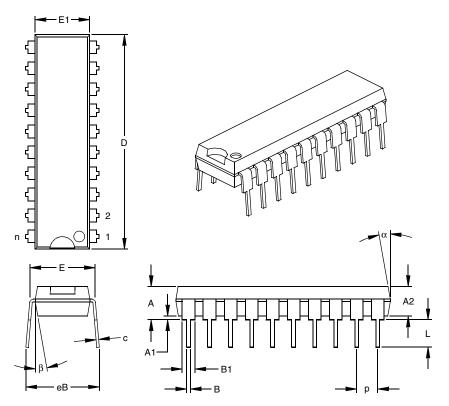

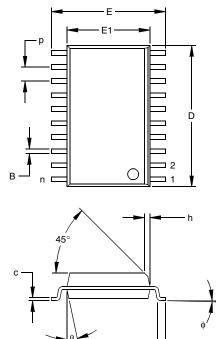

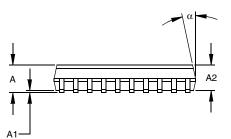

### 20-Lead Plastic Dual In-line (P) – 300 mil Body (PDIP)

|                            | Units    |       | INCHES* |       | Ν     | IILLIMETERS | 3     |

|----------------------------|----------|-------|---------|-------|-------|-------------|-------|

| Dimensio                   | n Limits | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |

| Number of Pins             | n        |       | 20      |       |       | 20          |       |

| Pitch                      | р        |       | .100    |       |       | 2.54        |       |

| Top to Seating Plane       | Α        | .140  | .155    | .170  | 3.56  | 3.94        | 4.32  |

| Molded Package Thickness   | A2       | .115  | .130    | .145  | 2.92  | 3.30        | 3.68  |

| Base to Seating Plane      | A1       | .015  |         |       | 0.38  |             |       |

| Shoulder to Shoulder Width | Е        | .295  | .310    | .325  | 7.49  | 7.87        | 8.26  |

| Molded Package Width       | E1       | .240  | .250    | .260  | 6.10  | 6.35        | 6.60  |

| Overall Length             | D        | 1.025 | 1.033   | 1.040 | 26.04 | 26.24       | 26.42 |